Арифметические сумматоры

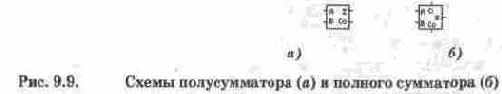

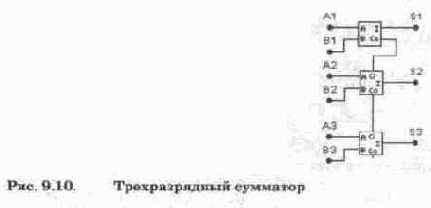

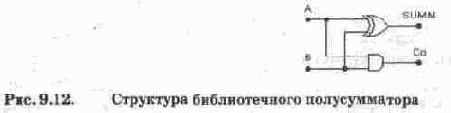

Арифметические сумматоры являются составной частью так называемых арифметико-логических устройств (АЛУ) микропроцессоров (МП). Они используются также для формирования физического адреса ячеек памяти в МП с сегментной организацией памяти. В программе EWB арифметические сумматоры представлены в библиотеке Comb'I двумя базовыми устройствами, показанными на рис. 9.9: полусумматором и полным сумматором. Они имеют следующие назначения выводов: А, В — входы слагаемых, ? — результат суммирования. Со — выход переноса, Ci — вход переноса. Многоразрядный сумматор создается на базе одного полусумматора и га полных сумматоров. В качестве примера на рис. 9.10 приведена структура трехразрядного сумматора [20]. На входы Al, A2, A3 и Bl, B2, ВЗ подаются первое и второе слагаемые соответственно, а с выходов SI, S2, S3 снимается результат суммирования.

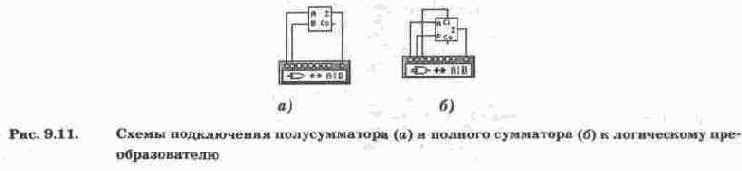

Для исследования внутренней структуры и логики функционирования сумматоров как нельзя лучше подходит логический преобразователь. После подключения полусумматора к преобразователю согласно рис. 9.11, а последовательно нажимаем кнопки

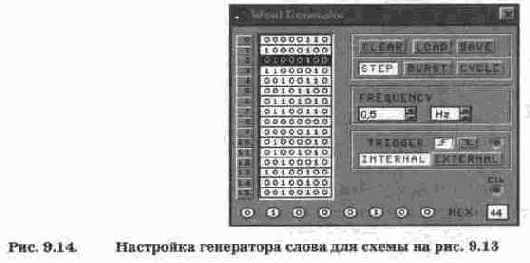

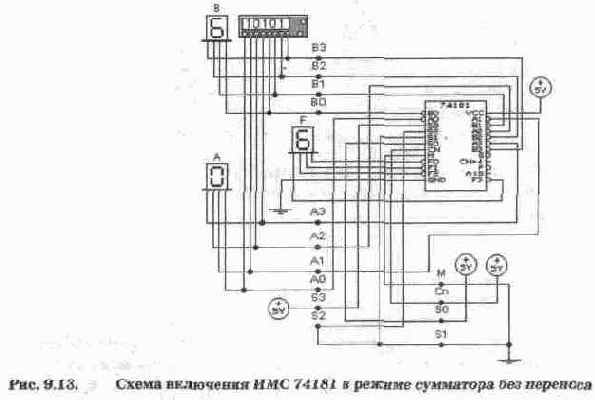

В каталоге программы EWB 4.1 имеется схема включения четырехразрядного АЛУ (файл alul81.ca4) на базе серийной микросхемы 74181 (отечественный аналог К155ИПЗ [5, 7]). В несколько переработанном виде она показана на рис. 9.13. ИМС 74181 обеспечивает 32 режима работы АЛУ в зависимости от состояния управляющих сигналов на входах М, SO...S3, а также допускает наращивание разрядности (вход CN и выход CN<4 для переносов). Показанная на рис. 9.13 схема включения ИМС соответствует режиму сумматора без переноса. Значения четырехразрядных операндов А и В на входе задаются с помощью генератора слова и в шестнадцатерич-ном коде отображаются одноименными алфавитно-цифровыми индикаторами. На выходах FO...F3 результат суммирования отображается индикатором F. Изменяя состояния сигналов на управляющих входах, можно промоделировать большинство функций АЛУ, используемых в микропроцессорах (см. разд. 5.14). Режимы работы генератора слова в схеме на рис. 9.13 и его кодовый набор показаны на рис. 9.14.

Контрольные вопросы и задания

1. Чем отличается полусумматор от полного сумматора?

2. Выясните внутреннюю структуру полного сумматора, пользуясь схемой его подключения к логическому преобразователю на рис. 9.11, б и принимая во внимание методику решения аналогичной задачи для полусумматора.

3. Используя опыт работы со схемой на рис. 9.13, подключите ко входам трехразрядного сумматора на рис. 9.10 генератор слова, а к выходам — алфавитно-циф-ровой индикатор с дешифратором и проверьте правильность его функционирования.

4. Проверьте работу ИМС 74181 в режиме сумматора с переносом (на вход Сп подайте сигнал логического нуля), в